# The First Sunway TaihuLight Performance Results for Parallel Simulated Annealing

# Stony Brook University

# Changnian Han<sup>1,3</sup>, Meng Guo<sup>3</sup> (Advisor), and Yuefan Deng<sup>1,2,3</sup> (Advisor)

- IACS Affiliate Student; Department of Applied Mathematics and Statistics, Stony Brook University, NY 11794, United States

- 2. IACS Affiliate Faculty; Department of Applied Mathematics and Statistics, Stony Brook University, NY 11794, United States

- 3. Shangdong Computer Science Center (National Supercomputer Center in Jinan), Jinan, Shandong 250101, China

# **Abstract**

The parallel simulated annealing (SA) algorithm requires to synchronize status of all cores in a certain amount of steps. During implementation, the communication costs lots of time on visiting memory and retrieving data from each core. The many-core machine has a shared memory for computing cores within a core group, which is feasible to run the parallel SA algorithm. We tested parallel SA algorithm with an optimization problem, Rastrigin function, on both a multi-core supercomputer, Sunway BlueLight of SW1600 16-core processors, and a many-core supercomputer, Sunway TaihuLight of SW26010 260-core processor, the fastest many-core supercomputer released in June 2016. We find the parallel SA algorithm always performs better on the many-core processor system and produces a greater speedup and efficiency than the multi-core processor system in any experiment setting.

# Introduction

The two major architectures of processors are homogeneous and heterogeneous architectures. The homogeneous processor consists of several identical processors on a single chip such as Sunway BlueLight multi-core supercomputer; the heterogeneous processor consists of both identical processors and dissimilar coprocessors such as Sunway TaihuLight many-core supercomputer, the successor of BlueLight that released in June 2016 as the top 1 fastest supercomputer in the world. When the dimension of parallel problem is large and requires many communication during computation, the many-core system is able to minimize the communication cost and produce a great speedup. The parallel SA algorithm is such kind of problem. We implement this problem as the first parallel SA algorithm application on the TaihuLight ever. To do comparisons, Sunway BlueLight is also used to implement the algorithm in different communication frequency.

The poster is structured as following: section 2 states the parallel SA algorithm and the testing objective function; section 3 introduced the architectures of BlueLight and TaihuLight supercomputers; section 4 express the numerical result; section 5 concludes TaihuLight's performance.

# **Algorithm Description & Objective Function**

The parallel SA algorithm consists five main components, objective function, move generation, cooling schedule, mixing strategy, and stopping condition.

# Objective Function

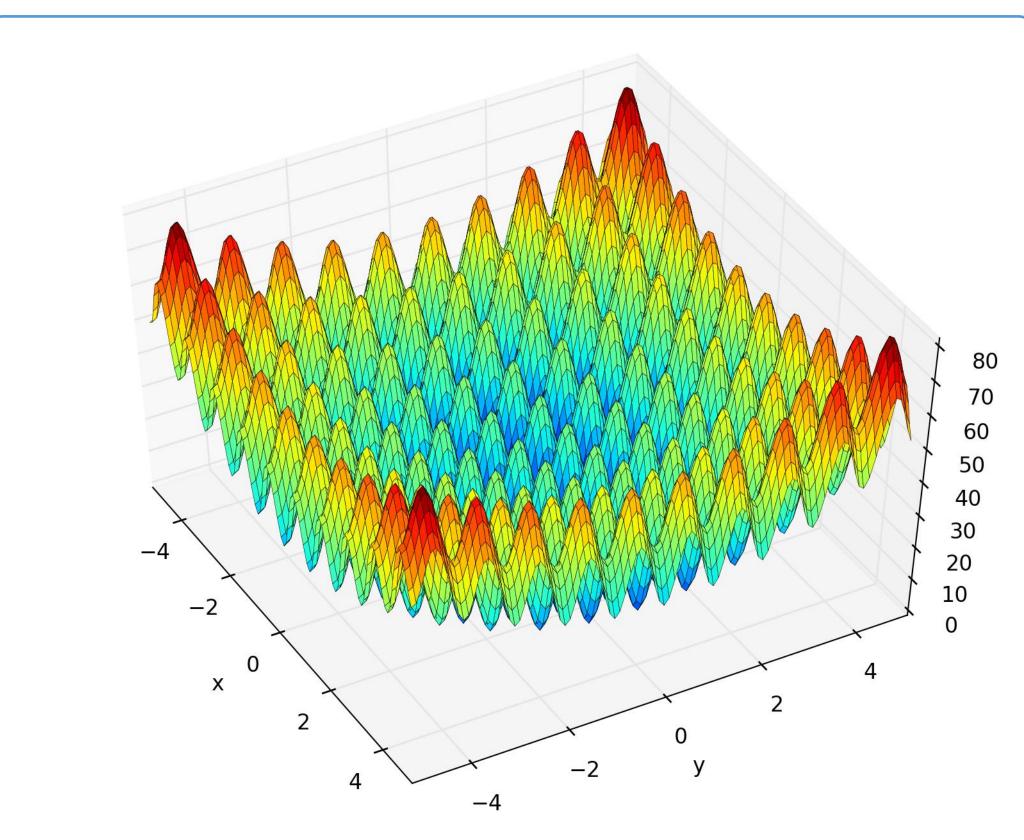

We use a benchmark optimization problem, Rastrigin function, as our objective function,

$$f(X) = An + \sum_{i=1}^{d} [x_i^2 - A\cos(2\pi x_i)]$$

where A is a constant, X is a d-dimensional vector and the global minimum is 0 at X = 0. Figure 1 gives a visualization of Rastrigin function with d = 2. In this project, we use A = 10, d = 1000, and  $x_i \in [-5.12, 5.12].$

# Moving Generation

In each step, the value of a random  $x_i$  is changed by a random scale and re-compute the objective function. Then the new states of Xand f(X) are accepted by probability.

# Cooling Schedule

Exponential cooling schedule:  $Temperature_n = \alpha^n Temperature_0$

Figure 1. The Rastrigin function with d=2.

## Mixing Period

We use the strategy introduced by Chu, Deng and Reinitz [1] in 1988, which produces full speedup on number of operation steps. It states each chain will randomly choose a target chain p to synchronize its states by probability

$$\frac{e^{-E_p/T}}{\sum_i e^{-E_i/T}}$$

where  $E_p$  is the objective function value, f(X), on chain p and T is the current temperature.

# Stopping Condition

Objective function value has no improvement in consecutive 500 steps.

# Sunway BlueLight & Sunway TaihuLight

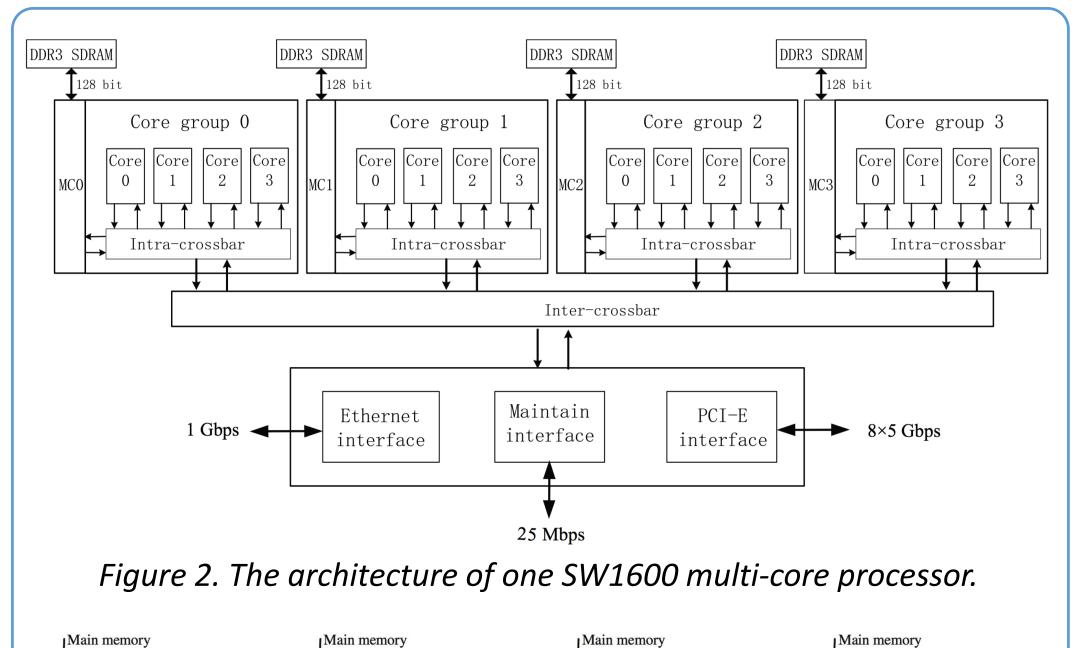

Sunway BlueLight is a homogeneous multi-core supercomputer released in 2011 as rank 14 supercomputer in the world. The main component of Sunway BlueLight is SW1600 [4] multi-core processor. As Figure 2 shows, each SW1600 processor consists of 4 core groups and each core group has 4 identical processing cores and own 4GB memory storage.

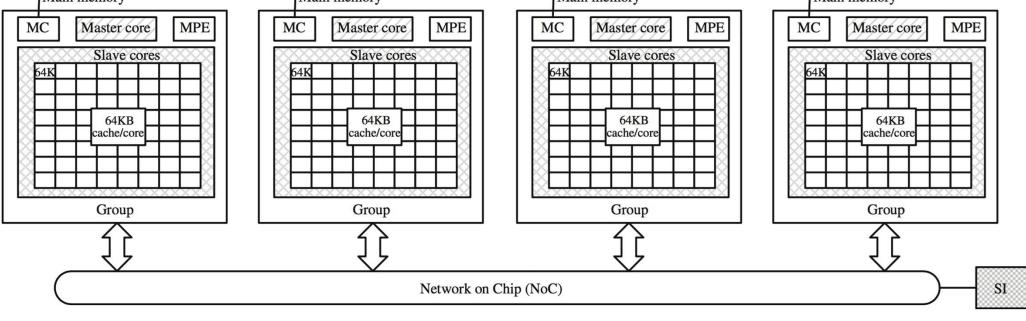

In June 2016, the successor of BlueLight, Sunway TihuLight, is released as the fastest heterogeneous many-core supercomputer in the world. Sunway TaihuLight is built up with SW26010 [2,3] many-core processors. As Figure 3 shows, each SW26010 processor also has 4 core groups. Differing from SW1600, each core group contains one management processing element (MPE) and one computing processing element (CPE) cluster, which integrated by 64 CPEs. MPE and CPEs share 8GB memory storage by connection to the memory control.

Sunway BlueLight distributes computing jobs to processing cores by MPI and communication may travel among core groups which is time consuming process. However, in Sunway TaihuLight, MPE assigns computing jobs to its large amount of slaves, CPEs, within one core group by threads. Since the memory is shared in the core group, sending and receiving data between CPEs can be done easily by visiting the shared memory directly. Thus, communication time is minimized.

Parallel SA algorithm searches the optimal solution by multiple Markov chains working independently and simultaneously. Lots of communication required to update states on each chain during process. The many-core Sunway TaihuLight is desired to solve this issue.

Figure 3. The architecture of one SW26010 many-core processor.

|                          | Sunway BlueLight<br>SW1600      | Sunway TaihuLight<br>SW26010   |

|--------------------------|---------------------------------|--------------------------------|

| Architecture             | Homogeneous<br>4 Core Groups    | Heterogeneous<br>4 Core Groups |

| Each Core Group          | 4 Identical<br>Processing Cores | 1 MPE<br>64 CPEs               |

| CPU Frequency            | 1.1GHz                          | 1.45GHz                        |

| Memory of one core group | 4GB                             | 8GB                            |

| Memory of one processor  | 16GB                            | 32GB                           |

| Peak<br>Performance      | 128GFlops                       | 3.06TFlops                     |

Table 1. Specifications of SW1600 and SW26010.

# **Performance Analysis**

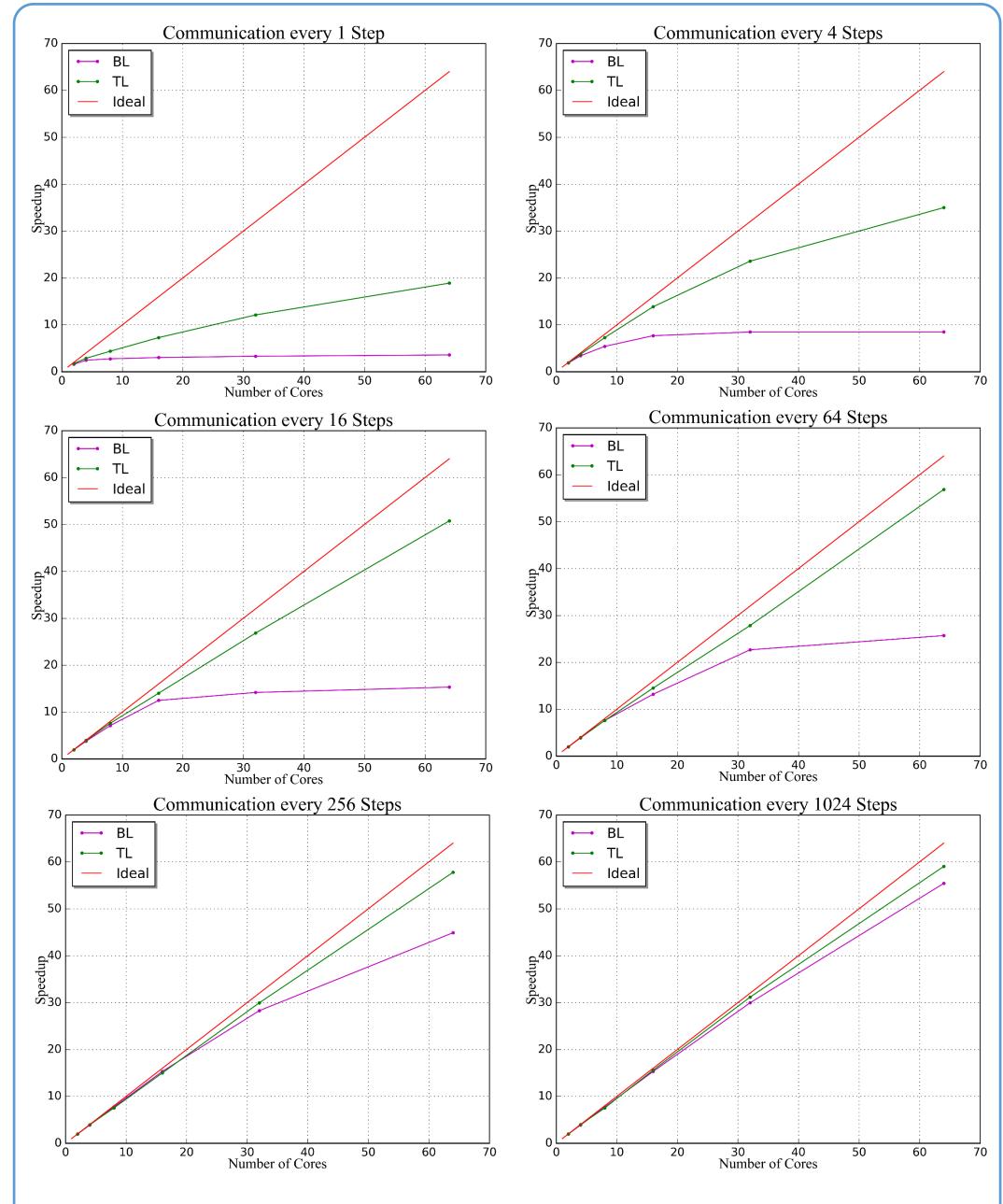

The experiment is implemented by utilizing 1, 2, 4 up to 64 cores, and for each setting, we fix the mixing period as 1, 4, 16 up to 1024 steps. Each pair of parameters is tested on both BlueLight and TaihuLight. The speedup curve is plotted in Figure 4.

Both systems cost a lot of time on communication when the mixing period is small. On multi-core system, the communication time will become comparable to the computing time. From the numerical result, the corresponding efficiency reduces quickly as the core count increases. Even though the communication frequency is high, the algorithm performs more than twice efficiency on TaihuLight compares with that on BlueLight in such cases since the communication within the core group always requires less time. While the mixing period grows, communication time consumption decreases. The result indicates the efficiency of BlueLight improves slowly and reaches its best performance as the mixing period goes to 1024, the lowest frequency. On the contrary, the efficiency of TaihuLight approaches 90% much faster than BlueLight and continues to perform better along with the frequency drops. In general, the parallel SA algorithm is more efficient on TaihuLight than BlueLight by shared memory architecture.

Figure 4. Performances of parallel SA algorithm on Sunway BlueLight (BL) and Sunway TaihuLight (TL).

# Conclusion

From analysis, we find the parallel SA algorithm can have a much better performance on the many-core supercomputer because of its CPE cluster architecture. The numerical result also indicates a greater speedup and efficiency for the algorithm on the many-core supercomputer than that on the multi-core supercomputer in any experiment setting.

# **References**

- [1] Chu, King-Wai, Yuefan Deng, and John Reinitz. "Parallel simulated annealing by mixing of states." Journal of Computational Physics 148.2 (1999): 646-662.

- [2] Dongarra, Jack. "Report on the Sunway TaihuLight system." PDF. Retrieved June 20 (2016).

- [3] Fu, Haohuan, et al. "The Sunway TaihuLight supercomputer: system and applications." Science China Information Sciences 59.7 (2016): 1-

- [4] Hu, Xiangdong, Jianxin Yang, and Ying Zhu, "Shenwei-1600: a high-performance multi-core microprocessor." Science China Information Sciences 004 (2015): 513-522.

# Acknowledgement

We thank for Haohuan Fu, associate director of National Supercomputer Center in Wuxi, for assistance. This research was partially supported by National Supercomputer Center in Wuxi, Wuxi 214072, China.